Si recién está comenzando a aprender cómo funcionan las CPU de múltiples núcleos, el almacenamiento en caché, la coherencia de la caché y la memoria, puede parecer un poco confuso al principio. Con eso en mente, la publicación de preguntas y respuestas de SuperUser de hoy tiene respuestas a la pregunta de un lector curioso.

La sesión de preguntas y respuestas de hoy nos llega por cortesía de SuperUser, una subdivisión de Stack Exchange, un grupo de sitios web de preguntas y respuestas impulsado por la comunidad.

La pregunta

El lector de superusuario CarmeloS quiere saber cuándo se vacía la memoria caché de una CPU a la memoria principal:

Si tengo una CPU con dos núcleos y cada núcleo tiene su propia caché L1, ¿es posible que Core1 y Core2 guarden en caché la misma parte de la memoria al mismo tiempo? Si es posible, ¿cuál será el valor de la memoria principal si tanto Core1 como Core2 han editado sus valores en la caché?

¿Cuándo se vacía la memoria caché de una CPU a la memoria principal?

La respuesta

Los colaboradores de superusuario David Schwartz, sleske y Kimberly W tienen la respuesta para nosotros. Primero, David Schwartz:

Si tengo una CPU con dos núcleos y cada núcleo tiene su propia caché L1, ¿es posible que Core1 y Core2 guarden en caché la misma parte de la memoria al mismo tiempo?

Sí, el rendimiento sería terrible si este no fuera el caso. Considere dos subprocesos que ejecutan el mismo código. Quieres ese código en ambas cachés L1.

Si es posible, ¿cuál será el valor de la memoria principal si tanto Core1 como Core2 han editado sus valores en la caché?

El valor anterior estará en la memoria principal, lo que no importará ya que ninguno de los núcleos lo leerá. Antes de expulsar un valor modificado de la caché, debe escribirse en la memoria. Normalmente, se utiliza alguna variante del protocolo MESI . En la implementación tradicional de MESI, si un valor se modifica en una caché, no puede estar presente en ninguna otra caché en ese mismo nivel.

Seguido de la respuesta de sleske:

Sí, tener dos cachés en la memoria caché de la misma región de memoria puede suceder y en realidad es un problema que ocurre mucho en la práctica. Hay varias soluciones, por ejemplo:

- Los dos cachés pueden comunicarse para asegurarse de que no estén en desacuerdo

- Puede tener algún tipo de supervisor que supervise todos los cachés y los actualice en consecuencia

- Cada procesador monitorea las áreas de memoria que ha almacenado en caché y, cuando detecta una escritura, descarta su caché (ahora no válido)

El problema se llama coherencia de caché y el artículo de Wikipedia sobre el tema tiene una buena descripción general del problema y sus posibles soluciones.

Y nuestra respuesta final de Kimberly W:

Para responder a la pregunta en el título de su publicación, depende del protocolo de almacenamiento en caché. Si es de escritura diferida, la caché solo se vaciará de nuevo a la memoria principal cuando el controlador de caché no tenga más remedio que colocar un nuevo bloque de caché en el espacio ya ocupado. El bloque que ocupaba anteriormente el espacio se elimina y su valor se vuelve a escribir en la memoria principal.

El otro protocolo es la escritura simultánea. En ese caso, cada vez que se escribe el bloque de caché en el nivel n , se actualiza el bloque correspondiente en el nivel n + 1 . Es similar en concepto a llenar un formulario con papel carbón debajo; todo lo que escriba en la parte superior se copiará en la hoja de abajo. Esto es más lento porque obviamente implica más operaciones de escritura, pero los valores entre cachés son más consistentes. En el esquema de escritura diferida, solo la caché de nivel más alto tendría el valor más actualizado para un bloque de memoria en particular.

¿Tiene algo que agregar a la explicación? Habla en los comentarios. ¿Quieres leer más respuestas de otros usuarios de Stack Exchange expertos en tecnología? Consulte el hilo de discusión completo aquí .

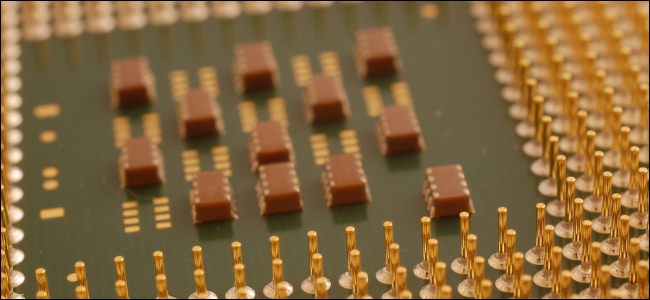

Crédito de la imagen: Lemsipmatt (Flickr)